- 品牌

- 京曉電路/京曉教育

- 型號

- 完整

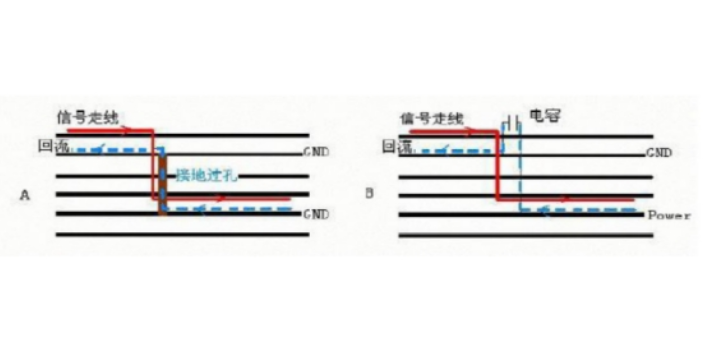

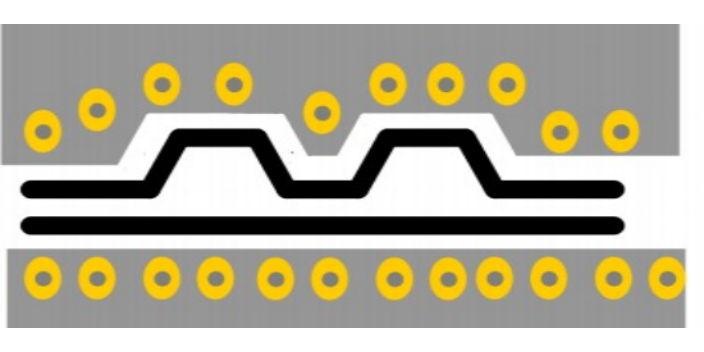

有利于元器件之間的布線工作,但是該方案的缺陷也較為明顯,表現為以下兩方面。①電源層和地線層分隔較遠,沒有充分耦合。②信號層Siganl_2(Inner_2)和Siganl_3(Inner_3)直接相鄰,信號隔離性不好,容易發生串擾。(2)Siganl_1(Top),Siganl_2(Inner_1),POWER(Inner_2),GND(Inner_3),Siganl_3(Inner_4),Siganl_4(Bottom)。方案2相對于方案1,電源層和地線層有了充分的耦合,比方案1有一定的優勢,但是Siganl_1(Top)和Siganl_2(Inner_1)以及Siganl_3(Inner_4)和Siganl_4(Bottom)信號層直接相鄰,信號隔離不好,容易發生串擾的問題并沒有得到解決。(3)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),POWER(Inner_3),GND(Inner_4),Siganl_3(Bottom)。相對于方案1和方案2,方案3減少了一個信號層,多了一個內電層,雖然可供布線的層面減少了,但是該方案解決了方案1和方案2共有的缺陷。①電源層和地線層緊密耦合。②每個信號層都與內電層直接相鄰,與其他信號層均有有效的隔離,不易發生串擾。③Siganl_2(Inner_2)和兩個內電層GND(Inner_1)和POWER(Inner_3)相鄰,可以用來傳輸高速信號。剛柔結合板:動態彎折萬次無損傷,適應可穿戴設備需求。武漢打造PCB制板

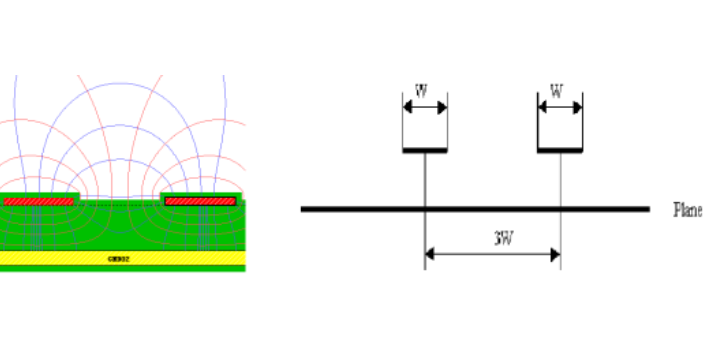

布線前的阻抗特征計算和信號反射的信號完整性分析,用戶可以在原理圖環境下運行SI仿真功能,對電路潛在的信號完整性問題進行分析,如阻抗不匹配等因素的信號完整性分析是在布線后PCB版圖上完成的,它不僅能對傳輸線阻抗、信號反射和信號間串擾等多種設計中存在的信號完整性問題以圖形的方式進行分析,而且還能利用規則檢查發現信號完整性問題,同時,AltiumDesigner還提供一些有效的終端選項,來幫助您選擇解決方案。2,分析設置需求在PCB編輯環境下進行信號完整性分析。為了得到精確的結果,在運行信號完整性分析之前需要完成以下步驟:1、電路中需要至少一塊集成電路,因為集成電路的管腳可以作為激勵源輸出到被分析的網絡上。像電阻、電容、電感等被動元件,如果沒有源的驅動,是無法給出仿真結果的。2、針對每個元件的信號完整性模型必須正確。3、在規則中必須設定電源網絡和地網絡,具體操作見本文。4、設定激勵源。5、用于PCB的層堆棧必須設置正確,電源平面必須連續,分割電源平面將無法得到正確分析結果,另外,要正確設置所有層的厚度。3,操作流程a.布線前(即原理圖設計階段)SI分析概述用戶如需對項目原理圖設計進行SI仿真分析。荊州正規PCB制板批發在現代電子技術的發展中,印刷電路板(PCB)制版無疑是一個至關重要的環節。

PCB制版,即印刷電路板的制版,對于現代電子設備的制造至關重要。在我們日常生活中,幾乎所有的電子產品,包括手機、電腦、電視等,背后都少不了這項技術的支持。印刷電路板作為電子元件的載體,通過將電路圖案精確地轉印到絕緣基材上,形成連接各個元件的關鍵通道。在PCB制版的過程中,首先需要設計出電路圖,這一步驟通常采用專業的電路設計軟件來完成。設計師根據產品的功能需求,精心布置每個元件的位置與連接線,力求使電路布局盡可能簡潔、有效。

兩個內電層可以有效地屏蔽外界對Siganl_2(Inner_2)層的干擾和Siganl_2(Inner_2)對外界的干擾。綜合各個方面,方案3顯然是化的一種,同時,方案3也是6層板常用的層疊結構。通過對以上兩個例子的分析,相信讀者已經對層疊結構有了一定的認識,但是在有些時候,某一個方案并不能滿足所有的要求,這就需要考慮各項設計原則的優先級問題。遺憾的是由于電路板的板層設計和實際電路的特點密切相關,不同電路的抗干擾性能和設計側重點各有所不同,所以事實上這些原則并沒有確定的優先級可供參考。但可以確定的是,設計原則2(內部電源層和地層之間應該緊密耦合)在設計時需要首先得到滿足,另外如果電路中需要傳輸高速信號,那么設計原則3(電路中的高速信號傳輸層應該是信號中間層,并且夾在兩個內電層之間)就必須得到滿足。目前印制板的品種已從單面板發展到雙面板、多層板和撓性板。

在高速數字系統中,由于脈沖上升/下降時間通常在10到幾百p秒,當受到諸如內連、傳輸時延和電源噪聲等因素的影響,從而造成脈沖信號失真的現象;在自然界中,存在著各種各樣頻率的微波和電磁干擾源,可能由于很小的差異導致高速系統設計的失敗;在電子產品向高密和高速電路設計方向發展,解決一系列信號完整性的問題,成為當前每一個電子設計者所必須面對的問題。業界通常會采用在PCB制板前期,通過信號完整性分析工具盡可能將設計風險降,從而也促進了EDA設計工具的發展……信號完整性(SignalIntegrity,簡稱SI)問題是指高速數字電路中,脈沖形狀畸變而引發的信號失真問題,通常由傳輸線阻抗不匹配產生的問題。而影響阻抗匹配的因素包括信號源的架構、輸出阻抗(outputimpedance)、走線的特性阻抗、負載端的特性、走線的拓樸(topology)架構等。解決的方式可以采用端接(termination)與調整走線拓樸的策略。信號完整性問題通常不是由某個單一因素導致的,而是板級設計中多種因素共同作用的結果。信號完整性問題主要表現形式包括信號反射、信號振鈴、地彈、串擾等;1,AltiumDesigner信號完整性分析(機理、模型、功能)在AltiumDesigner設計環境下。盲埋孔技術:隱藏式孔道設計,提升復雜電路空間利用率。襄陽生產PCB制板哪家好

PCB制版是一個復雜而精密的工藝過程。武漢打造PCB制板

Inner_1),GND(Inner_2),Siganl_2(Bottom)。(3)POWER(Top),Siganl_1(Inner_1),GND(Inner_2),Siganl_2(Bottom)。顯然,方案3電源層和地層缺乏有效的耦合,不應該被采用。那么方案1和方案2應該如何進行選擇呢?一般情況下,設計人員都會選擇方案1作為4層板的結構。選擇的原因并非方案2不可被采用,而是一般的PCB板都只在頂層放置元器件,所以采用方案1較為妥當。但是當在頂層和底層都需要放置元器件,而且內部電源層和地層之間的介質厚度較大,耦合不佳時,就需要考慮哪一層布置的信號線較少。對于方案1而言,底層的信號線較少,可以采用大面積的銅膜來與POWER層耦合;反之,如果元器件主要布置在底層,則應該選用方案2來制板。如果采用如圖11-1所示的層疊結構,那么電源層和地線層本身就已經耦合,考慮對稱性的要求,一般采用方案1。6層板在完成4層板的層疊結構分析后,下面通過一個6層板組合方式的例子來說明6層板層疊結構的排列組合方式和方法。(1)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),Siganl_3(Inner_3),POWER(Inner_4),Siganl_4(Bottom)。方案1采用了4層信號層和2層內部電源/接地層,具有較多的信號層。武漢打造PCB制板

CEM板材:玻璃纖維增強的酚醛樹脂材料,具有較高的機械強度和耐熱性,通常用于制作高頻電路板和高速電路板,因其具有較低的介電常數和介質損耗。高頻板材:采用聚四氟乙烯(PTFE)材料或其復合材料制成,具有較低的介電常數和介質損耗,適用于制作高頻電路板和高速電路板,常見厚度為0.8mm、1.0mm、1.2mm等。陶瓷基板:具有高熱導率、高溫穩定性、優良的電氣性能和較高的機械強度,但較脆,適用于高功率LED照明、RF和微波通信、航空航天和***電子設備等高頻、高速電路。埋容埋阻技術:集成無源器件,電路布局更簡潔高效。荊州焊接PCB制板布線PCB制版材料基板材料:FR - 4具有良好的絕緣性、耐熱性和機...

- 隨州專業PCB制板功能 2025-07-14

- 武漢正規PCB制板怎么樣 2025-07-14

- 黃石定制PCB制板哪家好 2025-07-13

- 隨州了解PCB制板報價 2025-07-13

- 鄂州專業PCB制板怎么樣 2025-07-13

- 咸寧PCB制板廠家 2025-07-13

- 黃岡定制PCB制板價格大全 2025-07-13

- 高速PCB制板價格大全 2025-07-12

- 鄂州設計PCB制板原理 2025-07-12

- 咸寧生產PCB制板批發 2025-07-12

- 武漢PCB制板批發 2025-07-11

- 武漢專業PCB制板哪家好 2025-07-11

- 鄂州生產PCB制板功能 2025-07-11

- 鄂州了解PCB制板功能 2025-07-11

- 武漢印制PCB制板價格大全 2025-07-10

- 湖北高速PCB制板 2025-07-10

- 武漢哪里的PCB培訓教程 07-14

- 孝感正規PCB設計原理 07-14

- 孝感焊接PCB制版廠家 07-14

- 十堰什么是PCB設計加工 07-14

- 荊州焊接PCB制板布線 07-14

- 深圳什么是PCB培訓哪家好 07-14

- 孝感生產PCB制版銷售 07-14

- 隨州設計PCB設計布局 07-14

- 隨州專業PCB制板功能 07-14

- 武漢正規PCB制板怎么樣 07-14