在跳變定時中,每個序列步驟只有2個分支。在跳變時序中,只有一個全局計數器可用。跳變時序需要有時間標簽才能重建數據。通過將時間標簽與內存中的測量數據交叉可存儲時間標簽。默認情況下,分析儀將查找為邏輯分析儀模塊定義的所有總線/信號上的轉變。但是,為增加可用內存深度和采集時間,可以在高級觸發中選擇不存儲某些總線/信號轉變(如將無用信息添加到測量中的時鐘或選沖信號)。運行測量時,無論總線/信號是否定義或是否分配給邏輯分析儀通道,都將在所有這些通道上采集數據。在跳變時序模式中,如果定義的總線/信號(未排除的)上存在轉變,將保存采集的樣本。運行跳變時序測量后。如果為以前未分配的邏輯分析儀通道定義新的總線/信號,那么將顯示在這些通道上采集的數據,但是不可能存儲這些總線/信號上的所有轉變;顯示的數據好似新的總線/信號在運行測量前就已經被排除了。在跳變時序中,不需要預先存儲數據(觸發前獲得的樣本)。因此,與狀態模式非常相似的是,觸發位置(起始/中心/結束)表明觸發后樣本占用內存的百分比。歐奧電子是Prodigy在中國區的官方授權合作伙伴,ProdigyMPHY,UniPro,UFS總線協議分析儀測試解決方案不會收到EAR進出口方面的管制。SD協議分析儀/訓練器找歐奧!武漢UART分析儀品牌

系統的電流負載能力一般在幾個KΩ以上,分流效應對系統的影響一般可以忽略,現在流行的幾種長邏輯分析儀探頭的阻抗一般在20~200KΩ之間。b、探頭的容性負載:容性負載就是探頭接入系統時,探頭的等效電容,這個值一般在1~30PF之間,在高速系統中,容性負載對電路的影響遠遠于阻性負載,如果這個值太,將會直接影響整個系統中的信號"沿"的形狀改變整個電路的性質,改變邏輯分析儀對系統觀測的實時性,導致我們看到的并不是系統原有的特性。c、探頭的易用性:是指探頭接入系統時的難易程度,隨著芯片封裝的密度越來越高,出現了BGA、QFP、TQFP、PLCC、SOP等各種各樣的封裝形式,IC的腳間距小的已達到,要很好的將信號引出,特別是BGA封裝,確實有困難,并且分立器件的尺寸也越來越小,典型的已達到×。d、與現有電路板上的調試部分的兼容性。6、系統的開放性:隨著數據共享的呼聲越來越高,我們所使用的系統的開放性就越來越重要,邏輯分析儀的操作系統也由過去的系統發展到使用Windows介面,這樣我們在使用時很方便。小結如果在你的工作中有數字邏輯信號,你就有機會使用邏輯分析儀。因此應選好一種邏輯分析儀,既符合所用的功能,又不太超越所需的功能。北京USB分析儀收費QSPI協議分析儀/訓練器找歐奧!

圖25阻尼電阻探測方式阻尼電阻阻值小的一般規則:目標阻抗的。如果探測環境需要更長的連線,這時候可考慮電阻匹配探測,即在探頭尖處附加一個匹配電阻,消除連線的反射。匹配電阻的阻值與連線傳輸線的阻抗一樣即可,但需要考慮信號的衰減。圖26電阻匹配探測方式邏輯分析儀的探頭主要有3種類型:提前設計型;事后考慮型;定制型。圖27邏輯分析儀的探頭類型小結:邏輯分析儀探頭是邏輯分析儀非常重要的部分,典型探頭的形狀,連接,參數如下圖所示。歐奧電子是Prodigy在中國區的官方授權合作伙伴,ProdigyMPHY,UniPro,UFS總線協議分析儀測試解決方案不會收到EAR進出口方面的管制。同時還有代理其他總類的協議分析儀,包括嵌入式設備用的SDIO協議分析儀,QSPI協議分析儀及訓練器。

序列的每個步驟被稱為一個序列步驟。每個序列步驟由兩部分組成:條件和操作。條件是指布爾邏輯表達式,例如“IfADDR=1000”或“IfthereisarisingedgeonSIG1”。操作是指符合條件時邏輯分析儀應當執行的內容。操作的示例包括觸發邏輯分析儀、轉至另一序列步驟以及啟動定時器。這類似于編程中的If/Then語句。觸發序列中的每個步驟都被指定一個數字。執行的個序列步驟總是序列步驟1,但由于“轉到”操作,剩余的序列步驟可以以任意順序執行。執行一個序列步驟且布爾邏輯表達式均為假時,邏輯分析儀將采集下一樣本并再次執行同一序列步驟于“KeepacquiringmoresamplesuntilDATA=7000,thentrigger”。如果符合一個序列步驟中的布爾邏輯表達式,那么在執行下一序列步驟之前總是采集另一樣本。換句話說,如果一個樣本符合序列步驟1的條件,在執行序列步驟2前將采集另一樣本。這意味著一個單獨的樣本不可能符合多個序列步驟的條中的條件二者之間采集了新的樣本,因此邏輯分析儀不會在采集樣本#1時觸發。可將此觸發序列看作是“FindADDR=1000followedbyDATA=2000andthentrigger”。觸發序列中的多序列步驟暗示了“后接”。邏輯分析儀觸發后,將不會再次觸發。換句話說。訓練器廠家哪家好?歐奧電子好!

將內存深度設置為值的一半(或更小)將返回Pod。在狀態采樣模式中,在選擇了高速狀態模式采樣選項的情況下,會將一個Pod對保留用于時間標簽存儲。在定時采樣模式中,在選擇了跳變/存儲限定定時模式采樣選項的情況下:選擇了小采樣周期時,會將一個Pod對保留用于時間標簽存儲。選擇了除小采樣周期之外的采樣周期時,選擇采集內存深度需要將一個Pod對保留用于時間標簽存儲。在這種情況下,將內存深度設置為值的一半(或更小)將返回Pod。該模塊是已分離的邏輯分析儀的一部分。在這種情況下,Pod位于分離分析儀的另一半模塊中。狀態模式和跳變定時模式下通道數、內存深度和觸發之間的相互影響:狀態采樣模式時,時間標簽存儲需要1個Pod或1/2的采集內存。在操作界面應用程序中,所有模塊都與時間相關;不能關閉timetagstorage(時間標簽存儲)(雖然以前的Agilent邏輯分析系統可以)。要使用1/2以上的模塊采集內存,必須將一個Pod保留用于時間標簽存儲。要使用所有Pod,內存使用量不能超過模塊采集內存的1/2。一般來說,可用定時器數與那些不屬于為時間標簽存儲而保留的Pod數相同。默認設置:時間標簽存儲始終處于開啟狀態(并且不能將其關閉)。SSIC協議分析儀/訓練器找歐奧!湖州SDIO分析儀收費

協議分析儀哪家強?歐奧強!武漢UART分析儀品牌

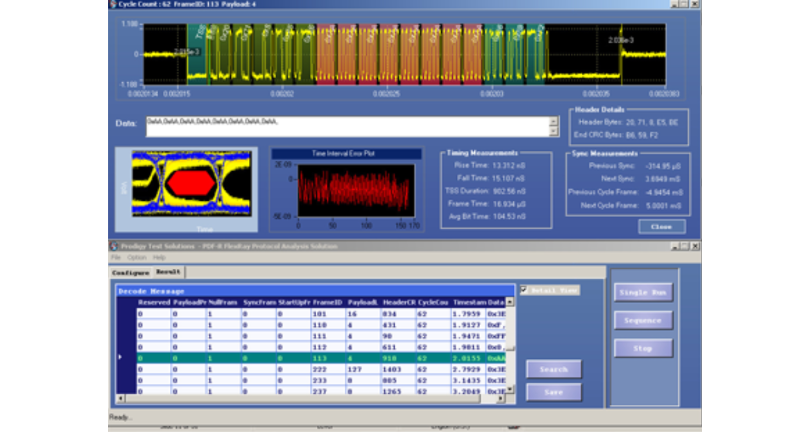

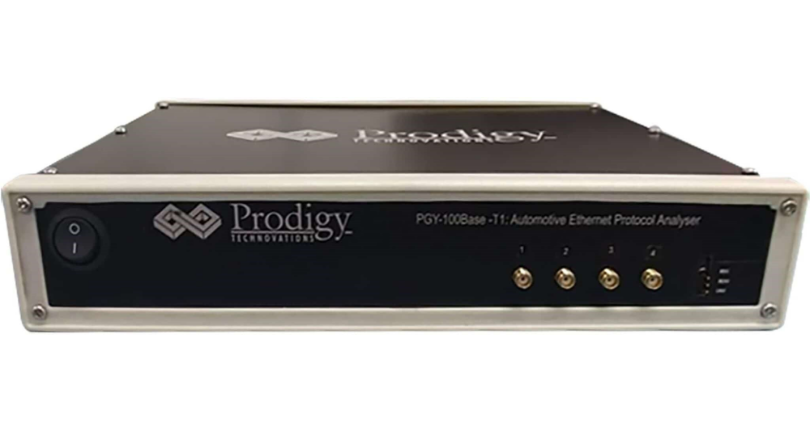

要采集地址,分析儀需要在MREQ線下降時進行采樣。要采集數據,分析儀需要在WR線下降(寫周期)或RD線下降(讀周期)時進行采樣。圖7狀態采集觸發狀態分析儀:與定時分析儀相似,狀態分析儀也具有限定要存儲的數據的功能。如果我們正在查找地址總線的上限和下限的特定碼型,當分析儀找到該碼型時,我們可以通知分析儀開始存儲,并且只要分析儀的內存未滿就一直存儲。歐奧電子是Prodigy在中國區的官方授權合作伙伴,ProdigyMPHY,UniPro,UFS總線協議分析儀測試解決方案不會收到EAR進出口方面的管制。同時還有代理其他總類的協議分析儀。包括嵌入式設備用的SDIO協議分析儀,QSPI協議分析儀及訓練器,I3C協議分析儀及訓練器,RFFE協議分析儀及訓練器等等。我司還有代理SPMI協議分析儀及訓練器,車載以太網分析儀,以及各種相關的基于示波器的解碼軟件和SI測試軟件。同時,歐奧電子也有提供高難度焊接,以及高速信號,如UFS,DDR3/DDR4,USBtypeC等高速協議抓取和分析的服務。簡單觸發示例:請看下面顯示的“D”觸發器,在正值的時鐘沿出現之前,“D”輸入上的數據是無效的。因此,時鐘輸入為上限時,觸發器的狀態才有效。圖8D觸發器現在,假設我們有并行的八個此類觸發器。如下所示。武漢UART分析儀品牌

邏輯分析的概念邏輯分析儀也是非常常用的儀表,與示波器一樣,是數字設計和測量的經典儀器之一。數字電路測...

【詳情】同時還有代理其他總類的協議分析儀,包括嵌入式設備用的SDIO協議分析儀,QSPI協議分析儀及訓練器,...

【詳情】歐奧電子也有提供高難度焊接,以及高速信號,如UFS,DDR3/DDR4,USBtypeC等高速協議抓...

【詳情】模擬器在執行模擬功能時使用。大容量存儲器用于保存監視器和模擬器的設定條件清單、模擬過程的程序和捕獲存...

【詳情】軟件使用運行Saleae軟件,此時邏輯分析儀的硬件已經與電腦相連,軟件會顯示[Connected]。...

【詳情】AOC27G2電競顯示器的白點色溫穩定在7300K,色溫整體稍微有些偏冷。以上便是此次帶來的AOC2...

【詳情】