-

黃石設(shè)計(jì)PCB設(shè)計(jì)哪家好

電源電路放置優(yōu)先處理開關(guān)電源模塊布局,并按器件資料要求設(shè)計(jì)。RLC放置(1)濾波電容放置濾波電容靠近管腳擺放(BGA、SOP、QFP等封裝的濾波電容放置),多與BGA電源或地的兩個(gè)管腳共用同一過(guò)孔。BGA封裝下放置濾波電容:BGA封裝過(guò)孔密集很難把所有濾波電容靠近管腳放置,優(yōu)先把電源、地進(jìn)行合并,且合并的管腳不能超過(guò)2個(gè),充分利用空管腳,...

查看詳細(xì) >>06 2023-03 -

宜昌什么是PCB設(shè)計(jì)銷售電話

電氣方面注意事項(xiàng)(1)TVS管、ESD、保險(xiǎn)絲等保護(hù)器件靠近接口放置;(2)熱敏器件遠(yuǎn)離大功率器件布局;(3)高、中、低速器件分區(qū)布局;(4)數(shù)字、模擬器件分區(qū)布局;(5)電源模塊、模擬電路、時(shí)鐘電路、射頻電路、隔離器件布局按器件資料;(6)串聯(lián)電阻靠近源端放置;串聯(lián)電容靠近末端放置;并聯(lián)電阻靠近末端放置;(7)退藕電容靠近芯片的電源管腳...

查看詳細(xì) >>06 2023-03 -

恩施定制PCB設(shè)計(jì)包括哪些

生成Gerber文件(1)生成Gerber文件:根據(jù)各EDA軟件操作,生成Gerber文件。(2)檢查Gerber文件:檢查Gerber文件步驟:種類→數(shù)量→格式→時(shí)間。Gerber文件種類及數(shù)量:各層線路、絲印層、阻焊層、鋼網(wǎng)層、鉆孔表、IPC網(wǎng)表必須齊全且不能重復(fù)。盲埋孔板或背鉆板輸出的鉆孔文件個(gè)數(shù)與孔的類型有關(guān),有多少種盲埋孔或背鉆...

查看詳細(xì) >>06 2023-03 -

隨州高效PCB設(shè)計(jì)廠家

PCBLAYOUT規(guī)范PCBLayout整個(gè)流程是:網(wǎng)表導(dǎo)入-結(jié)構(gòu)繪制-設(shè)計(jì)規(guī)劃-布局-布線-絲印調(diào)整-Gerber輸出。1.1網(wǎng)表導(dǎo)入網(wǎng)表導(dǎo)入子流程如下:創(chuàng)建PCB文件→設(shè)置庫(kù)路徑→導(dǎo)入網(wǎng)表。創(chuàng)建PCB文件(1)建立一個(gè)全新PCBLayout文件,并對(duì)其命名。(2)命名方式:“項(xiàng)目名稱+日期+版本狀態(tài)”,名稱中字母全部大寫,以日期加上版...

查看詳細(xì) >>06 2023-03 -

孝感高效PCB設(shè)計(jì)怎么樣

DDR的PCB布局、布線要求1、DDR數(shù)據(jù)信號(hào)線的拓?fù)浣Y(jié)構(gòu),在布局時(shí)保證緊湊的布局,即控制器與DDR芯片緊湊布局,需要注意DDR數(shù)據(jù)信號(hào)是雙向的,串聯(lián)端接電阻放在中間可以同時(shí)兼顧數(shù)據(jù)讀/寫時(shí)良好的信號(hào)完整性。2、對(duì)于DDR信號(hào)數(shù)據(jù)信號(hào)DQ是參考選通信號(hào)DQS的,數(shù)據(jù)信號(hào)與選通信號(hào)是分組的;如8位數(shù)據(jù)DQ信號(hào)+1位數(shù)據(jù)掩碼DM信號(hào)+1位數(shù)據(jù)...

查看詳細(xì) >>05 2023-03 -

武漢常規(guī)PCB設(shè)計(jì)哪家好

ADC和DAC是數(shù)字信號(hào)和模擬信號(hào)的接口,在通信領(lǐng)域,射頻信號(hào)轉(zhuǎn)換為中頻信號(hào),中頻信號(hào)經(jīng)過(guò)ADC轉(zhuǎn)換成數(shù)字信號(hào),經(jīng)過(guò)數(shù)字算法處理后,再送入DAC轉(zhuǎn)換成中頻,再進(jìn)行了變頻為射頻信號(hào)發(fā)射出去。(1)ADC和DAC的PCBLAYOUT1、布局原則:優(yōu)先兼顧ADC、DAC前端模擬電路,嚴(yán)格按照原理圖電路順序呈一字型對(duì)ADC、DAC前端模擬電路布局...

查看詳細(xì) >>05 2023-03 -

黃石如何PCB設(shè)計(jì)價(jià)格大全

規(guī)則設(shè)置子流程:層疊設(shè)置→物理規(guī)則設(shè)置→間距規(guī)則設(shè)置→差分線規(guī)則設(shè)置→特殊區(qū)域規(guī)則設(shè)置→時(shí)序規(guī)則設(shè)置◆層疊設(shè)置:根據(jù)《PCB加工工藝要求說(shuō)明書》上的層疊信息,在PCB上進(jìn)行對(duì)應(yīng)的規(guī)則設(shè)置。◆物理規(guī)則設(shè)置(1)所有阻抗線線寬滿足《PCB加工工藝要求說(shuō)明書》中的阻抗信息,非阻抗線外層6Mil,內(nèi)層5Mil。(2)電源/地線:線寬>=15Mil...

查看詳細(xì) >>05 2023-03 -

荊州定制PCB設(shè)計(jì)

通過(guò)規(guī)范PCBLayout服務(wù)操作要求,提升PCBLayout服務(wù)質(zhì)量和保證交期的目的。適用范圍適用于我司PCBLayout業(yè)務(wù)。文件維護(hù)部門設(shè)計(jì)部。定義與縮略語(yǔ)(1)PCBLayout:利用EDA軟件將邏輯原理圖設(shè)計(jì)為印制電路板圖的全過(guò)程。(2)PCB:印刷電路板。(3)理圖:一般由原理圖設(shè)計(jì)工具繪制,表達(dá)硬件電路中各種器件之間的連接關(guān)...

查看詳細(xì) >>05 2023-03 -

黃岡高速PCB設(shè)計(jì)功能

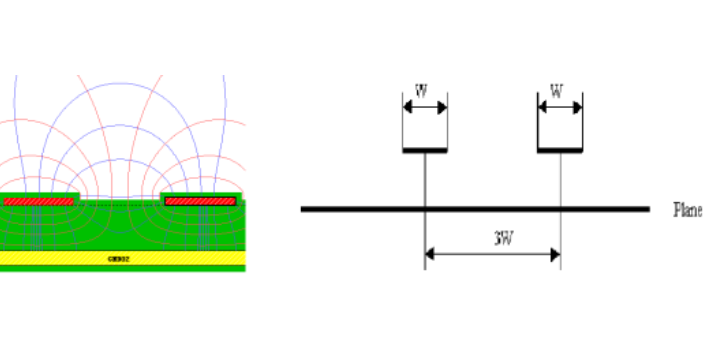

等長(zhǎng)線處理等長(zhǎng)線處理的步驟:檢查規(guī)則設(shè)置→確定組內(nèi)長(zhǎng)線段→等長(zhǎng)線處理→鎖定等長(zhǎng)線。(1)檢查組內(nèi)等長(zhǎng)規(guī)則設(shè)置并確定組內(nèi)基準(zhǔn)線并鎖定。(2)單端蛇形線同網(wǎng)絡(luò)走線間距S≥3W,差分對(duì)蛇形線同網(wǎng)絡(luò)走線間距≥20Mil。(3)差分線對(duì)內(nèi)等長(zhǎng)優(yōu)先在不匹配端做補(bǔ)償,其次在中間小凸起處理,且凸起高度<1倍差分對(duì)內(nèi)間距,長(zhǎng)度>3倍差分線寬,(4)差分線對(duì)...

查看詳細(xì) >>04 2023-03 -

宜昌PCB設(shè)計(jì)價(jià)格大全

PCBLAYOUT規(guī)范PCBLayout整個(gè)流程是:網(wǎng)表導(dǎo)入-結(jié)構(gòu)繪制-設(shè)計(jì)規(guī)劃-布局-布線-絲印調(diào)整-Gerber輸出。1.1網(wǎng)表導(dǎo)入網(wǎng)表導(dǎo)入子流程如下:創(chuàng)建PCB文件→設(shè)置庫(kù)路徑→導(dǎo)入網(wǎng)表。創(chuàng)建PCB文件(1)建立一個(gè)全新PCBLayout文件,并對(duì)其命名。(2)命名方式:“項(xiàng)目名稱+日期+版本狀態(tài)”,名稱中字母全部大寫,以日期加上版...

查看詳細(xì) >>04 2023-03 -

常規(guī)PCB設(shè)計(jì)教程

存儲(chǔ)模塊介紹:存儲(chǔ)器分類在我們的設(shè)計(jì)用到的存儲(chǔ)器有SRAM、DRAM、EEPROM、Flash等,其中DDR系列用的是多的,其DDR-DDR4的詳細(xì)參數(shù)如下:DDR采用TSSOP封裝技術(shù),而DDR2和DDR3內(nèi)存均采用FBGA封裝技術(shù)。TSSOP封裝的外形尺寸較大,呈長(zhǎng)方形,其優(yōu)點(diǎn)是成本低、工藝要求不高,缺點(diǎn)是傳導(dǎo)效果差,容易受干擾,散熱...

查看詳細(xì) >>04 2023-03 -

荊州打造PCB設(shè)計(jì)多少錢

DDR2模塊相對(duì)于DDR內(nèi)存技術(shù)(有時(shí)稱為DDRI),DDRII內(nèi)存可進(jìn)行4bit預(yù)讀取。兩倍于標(biāo)準(zhǔn)DDR內(nèi)存的2BIT預(yù)讀取,這就意味著,DDRII擁有兩倍于DDR的預(yù)讀系統(tǒng)命令數(shù)據(jù)的能力,因此,DDRII則簡(jiǎn)單的獲得兩倍于DDR的完整的數(shù)據(jù)傳輸能力;DDR采用了支持2.5V電壓的SSTL-2電平標(biāo)準(zhǔn),而DDRII采用了支持1.8V電壓...

查看詳細(xì) >>04 2023-03